同步操作将从 Gitee 极速下载/Verilator 强制同步,此操作会覆盖自 Fork 仓库以来所做的任何修改,且无法恢复!!!

确定后同步将在后台操作,完成时将刷新页面,请耐心等待。

|

|

|

|

|

|

|

|

|

|

Verilator is invoked with parameters similar to GCC or Synopsys's VCS. It "Verilates" the specified Verilog or SystemVerilog code by reading it, performing lint checks, and optionally inserting assertion checks and coverage-analysis points. It outputs single- or multithreaded .cpp and .h files, the "Verilated" code.

These Verilated C++/SystemC files are then compiled by a C++ compiler (gcc/clang/MSVC++), optionally along with a user's own C++/SystemC wrapper file, to instantiate the Verilated model. Executing the resulting executable performs the design simulation. Verilator also supports linking Verilated generated libraries, optionally encrypted, into other simulators.

Verilator may not be the best choice if you are expecting a full-featured replacement for a closed-source Verilog simulator, needs SDF annotation, mixed-signal simulation, or are doing a quick class project (we recommend Icarus Verilog for classwork.) However, if you are looking for a path to migrate SystemVerilog to C++/SystemC, or want high-speed simulation of designs, Verilator is the tool for you.

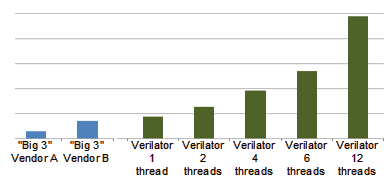

Verilator does not directly translate Verilog HDL to C++ or SystemC. Rather, Verilator compiles your code into a much faster optimized and optionally thread-partitioned model, which is in turn wrapped inside a C++/SystemC module. The results are a compiled Verilog model that executes even on a single-thread over 10x faster than standalone SystemC, and on a single thread is about 100 times faster than interpreted Verilog simulators such as Icarus Verilog. Another 2-10x speedup might be gained from multithreading (yielding 200-1000x total over interpreted simulators).

Verilator has typically similar or better performance versus the closed-source Verilog simulators (e.g., Carbon Design Systems Carbonator, Modelsim/Questa, Cadence Incisive/NC-Verilog, Synopsys VCS, VTOC, and Pragmatic CVer/CVC). But, Verilator is open-sourced, so you can spend on computes rather than licenses. Thus, Verilator gives you the best simulation cycles/dollar.

For more information:

Verilator is a community project, guided by the CHIPS Alliance under the Linux Foundation.

We appreciate and welcome your contributions in whatever form; please see Contributing to Verilator. Thanks to our Contributors and Sponsors.

Verilator also supports and encourages commercial support models and organizations; please see Verilator Commercial Support.

Verilator is Copyright 2003-2023 by Wilson Snyder. (Report bugs to Verilator Issues.)

Verilator is free software; you can redistribute it and/or modify it under the terms of either the GNU Lesser General Public License Version 3 or the Perl Artistic License Version 2.0. See the documentation for more details.

此处可能存在不合适展示的内容,页面不予展示。您可通过相关编辑功能自查并修改。

如您确认内容无涉及 不当用语 / 纯广告导流 / 暴力 / 低俗色情 / 侵权 / 盗版 / 虚假 / 无价值内容或违法国家有关法律法规的内容,可点击提交进行申诉,我们将尽快为您处理。